This project provides a functional simulation of a simplified MIPS CPU pipeline, focusing on certain core instructions and modules. The MIPS architecture is a Reduced Instruction Set Computer (RISC) instruction set, which provides for a more straightforward hardware design than Complex Instruction Set Computers (CISC).

Key Features:

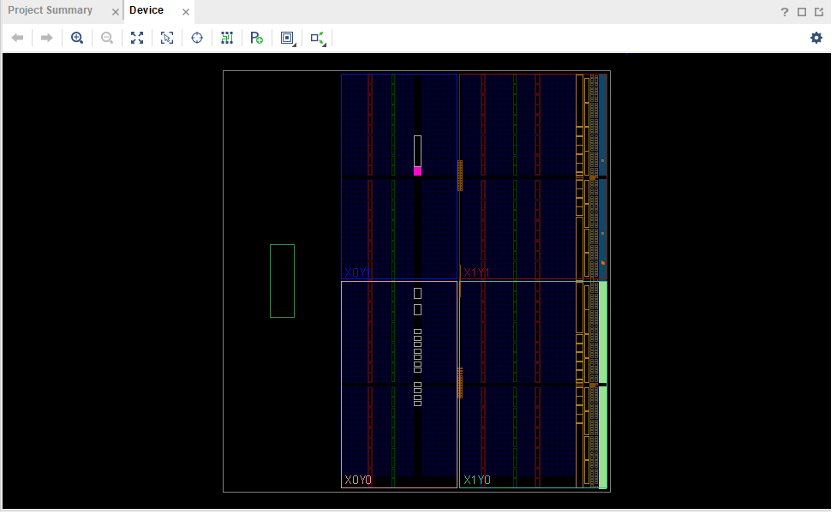

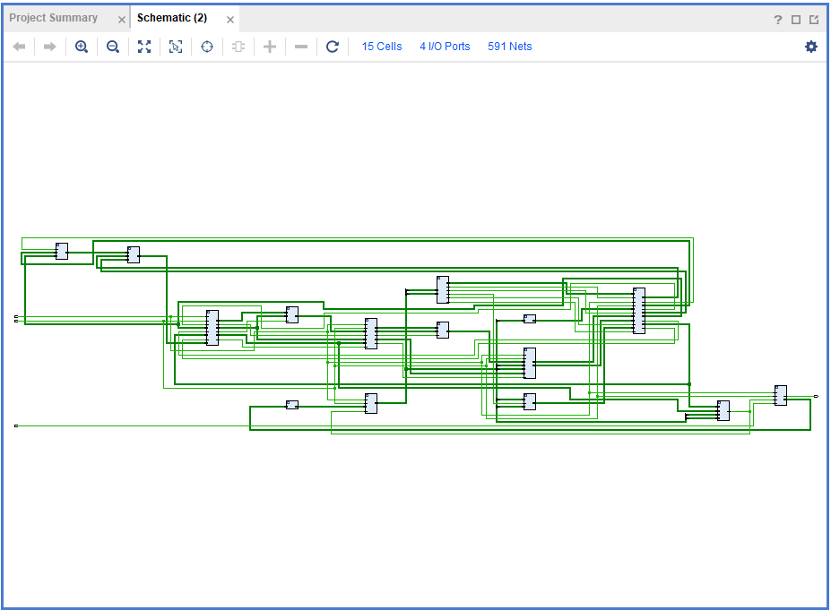

Five-stage Pipeline: The simulator incorporates the five-stage instruction pipeline of MIPS: Fetch, Decode, Execute, Memory, and Write-back.

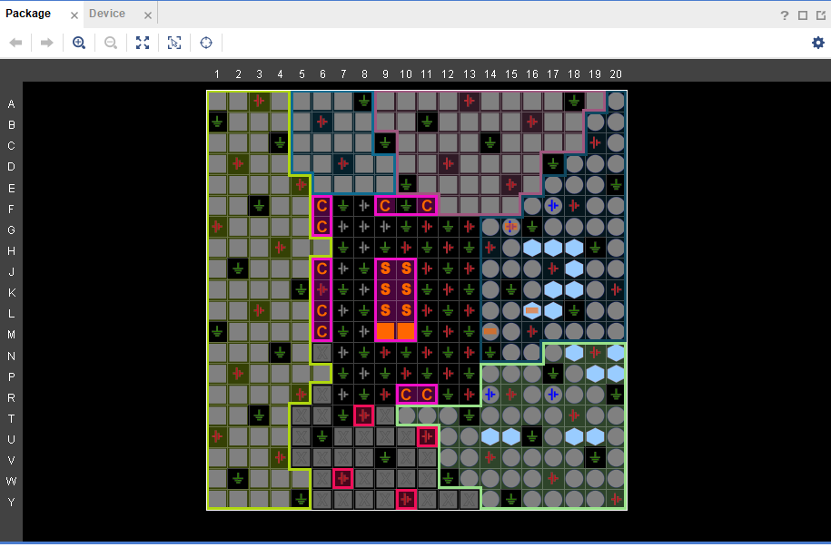

Modules:

Instruction Fetch (IF): Fetches instructions for processing.

Register File: A module that simulates the behavior of the CPU registers and their interaction with instructions.

Control: This module sets flags and control lines depending on the instruction opcode and function.

ALU (Arithmetic Logic Unit): This handles arithmetic and logic operations.

Data Memory: Simulates the data memory for load and store operations.

Multiplexers: Assists in making decisions for data paths based on control flags.

Sign Extension: Extends the immediate field to 32-bits.

Pipeline Registers: Ensures smooth data flow between pipeline stages.

Supported Instructions:

R-type Instructions: Supported operations include ADD, SUB, AND, OR, XOR.

I-type Instructions: The instruction of interest is 'lw' (load word).

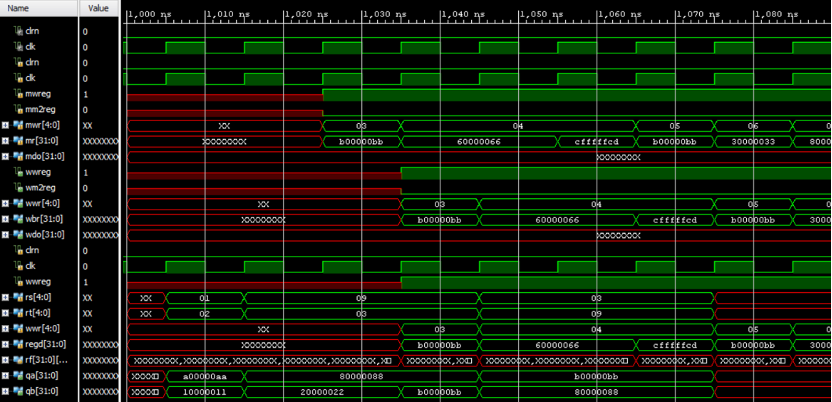

Testbench & Tester:

Testbench: The environment used to test the entire MIPS pipeline.

Tester: Generates the required clock and reset signals for the system.

Challenges Overcome:

Pipeline Hazards: Addressed potential hazards by implementing stall and flush mechanisms.

Modular Design: The code has been written in a modular manner, allowing for easy expansion and support for additional MIPS instructions in the future.

Debugging: Extensive testing and debugging ensured accuracy in operations and data flow.

Tools & Technologies:

HDL: Verilog

Simulator: (Assumed tool, e.g., ModelSim, Xilinx Vivado, etc.)

The MIPS Pipeline Simulator successfully simulated the key operations of the MIPS architecture. This simulation can be extended to support more complex scenarios, such as data and control hazards, branch prediction, and the inclusion of more MIPS instructions.